Original Assignee International Business Machines Corp Priority date (The priority date is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation or warranty as to the accuracy of the list.) Bulzacchelli Ankur Agrawal Current Assignee (The listed assignees may be inaccurate. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.) Active Application number US13/947,224 Other versions US20130300481A1

#WHEN DOES AN EDGE TRIGGERED FLIP FLOP CHANGE STATES PDF#

Google Patents Edge selection techniques for correcting clock duty cycleĭownload PDF Info Publication number US8686764B2 US8686764B2 US13/947,224 US201313947224A US8686764B2 US 8686764 B2 US8686764 B2 US 8686764B2 US 201313947224 A US201313947224 A US 201313947224A US 8686764 B2 US8686764 B2 US 8686764B2 Authority US United States Prior art keywords edge circuit output clock signal input Prior art date Legal status (The legal status is an assumption and is not a legal conclusion.

Google Patents US8686764B2 - Edge selection techniques for correcting clock duty cycle Professor Saha teaches subjects related to digital electronics & microprocessors.US8686764B2 - Edge selection techniques for correcting clock duty cycle Saha, who is an assistant professor in a renowned degree engineering college in India. The use of this J-K transition table (Table1) is a principal part of the synchronous counter design procedure. Thus, K must be a 0 while J can be at either level. Thus, K must be a 1, but J can be at either level.ġ to 1 transition: The PRESENT state is a 1 and is to remain a 1, which can happen when either J = K = 0 or J = 1 and K = 0. Thus, J must be a 1, but K can be at either level for this transition to occur.ġ to 0 transition: The PRESENT state is 1 and is to change to a 0, which can happen when either J = 0 and K = 1 or J = K = 1.

Recall that “ x” means the don’t-care condition.Ġ to 1 transition: The PRESENT state is 0 and is to change to a 1, which can happen when either J = 1 and K = 0 (set condition) or J = K = 1 (toggle condition). The table indicates this with a “0” under J and an “ x” under K. Thus, J must be at 0, but K can be at either level. From our understanding of how a J-K flip-flop works, this can happen when either J = K = 0 (no-change condition) or J = 0 and K = 1 (clear condition). The operation of the J-K flip-flop using the Transition table is explained below:Ġ to 0 transition : The FF PRESENT state is at 0 and is to remain at 0 when a clock pulse is applied. The last column list the J and K levels required to produce each transition. This column list the FF’s PRESENT state, symbolized as QN, and the NEXT state, symbolized as QN+1, for each transition. The leftmost column of this table lists each possible FF output transition. Table1: J -K Excitation Table OR J -K Transition Table Here is the operation of the J-K flip-flop using a different approach, one called an excitation table (Table 1).

J-K Excitation Table or J-K Transition Table

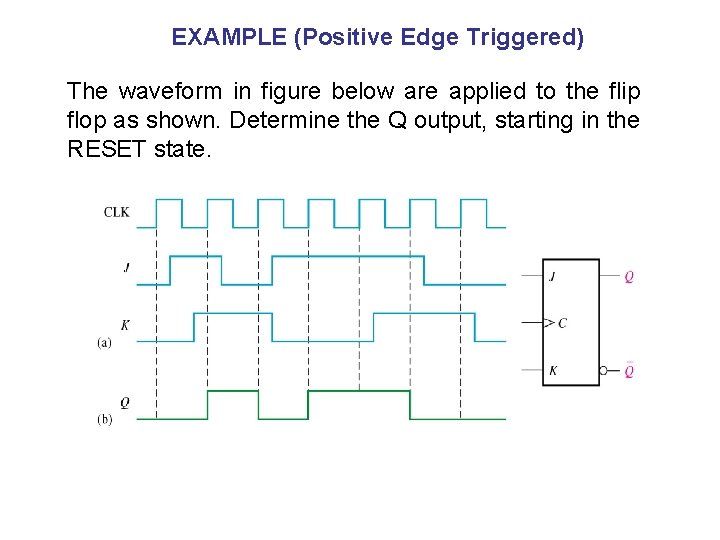

Explain the operation of the J-K flip-flop with its excitation table. We must review the operation of the J-K flip-flop using a different approach, one called an excitation table or transition table. The J and K inputs can be changed at any time when the clock input is LOW or HIGH (except for a very short intervalĪround the triggering transition of the clock) without affecting the output. Remember, the flip-flop cannot change state except on the triggering edge of a clock pulse. When J and K are both HIGH, the flip-flop changes state. When both J and K are LOW, the output does not change from its prior state. When J is LOW and K is HIGH, the Q output goes LOW on the triggering edge of the clock pulse, and the flip-flop is RESET. When J is HIGH and K is LOW, the Q output goes HIGH on the triggering edge of the clock pulse, and the flip-flop is SET. Figure1.2 Operation of a positive edge-triggered J-K flip-flop

0 kommentar(er)

0 kommentar(er)